|

部品実験 | 元に戻る |

| ADS1115(注意点あり) 2024/11/01 |

|

| |||||||

|

1.概要 2.簡単に使う 3.クイックガイド(データシート) 4.I2Cスレーブアドレス 5.レジスタ (1)ポインタレジスタ (2)変換レジスタ (3)設定レジスタ (4)閾値レジスタ (Lo_thresh 0x02 and Hi_thresh 0x03 Registers) 6.注意事項 他の機器故障拡大! |

1.ADS1115 Arduinoプログラム 2.ADS1115 Pythonプログラム(RaspberrPi) |

| 本 文 |

1.概要

(3)定格補足 a.アナログ最大入力電圧 VDD+03V b.コモンモード入力インピーダンス

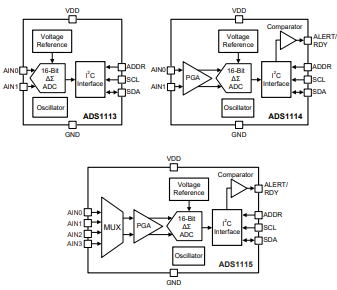

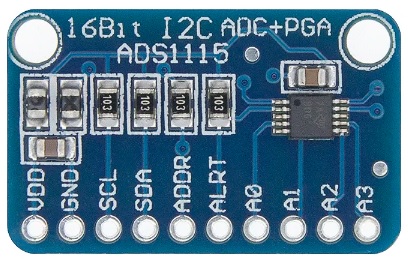

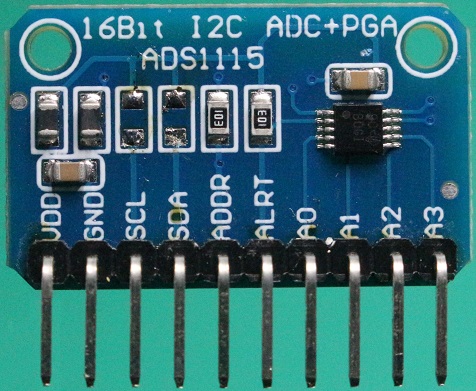

(4)概要 ADS1113、ADS1114、ADS1115デバイス (ADS111x)は、高精度、低消費電力、16ビット、I2C互換のA/Dコンバータ (ADC) です。超小型のリードレスX2QFN-10パッケージとVSSOP-10パッケージで供給されます。 ADS111xデバイスは低ドリフト基準電圧とオシレータを内蔵しています。 ADS1114とADS1115は、プログラマブル・ゲイン・アンプ (PGA) とデジタル・コンパレータも内蔵しています。これらの機能を有し動作電源電圧範囲が広いADS111xは、省電力と省スペースが要求される、センサを使用した測定アプリケーションに適します。 ADS111xは最大で860サンプル/秒 (SPS) までのデータ・レートで変換処理を実行できます。PGAは入力電圧範囲が±256mV~±6.144Vであり、振幅の小さな信号から大きな信号まで高精度に測定できます。 ADS1115には入力マルチプレクサ(MUX)が使用されており、2つの差動入力または4つのシングルエンド入力を測定できます。 過電圧や低電圧の検出には、ADS1114とADS1115のデジタル・コンパレータを使用してください。 ADS111xは、連続変換モードまたはシングル・ショット・モードで動作します。シングル・ショット・モード時は、1回の変換動作後にデバイスの電源が自動的にオフになるため、アイドリング中の消費電力を大幅に低減できます。 (5)ピン

|

|

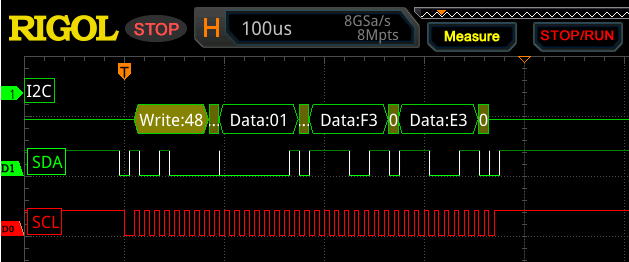

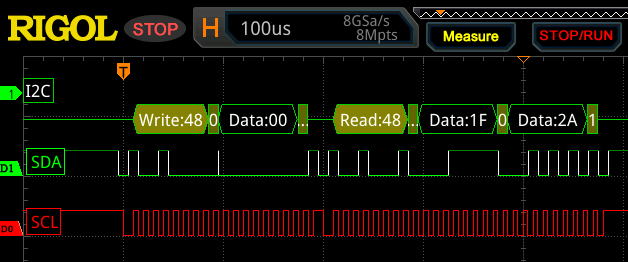

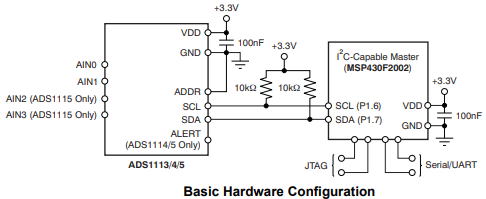

| 3.クイックスタートガイド(データシートの内容) このセクションでは、ADS1113/4/5通信の簡単な例を示します。 より詳細な説明については、このデータシートのセクションを参照してください。 この設計のハードウェアには、次のものが含まれます。 1001000のI2Cアドレスで構成された1つのADS1113/4/5。 I2Cインターフェイスを備えたマイクロコントローラー(TIはMSP430F2002を推奨)。 抵抗器、コンデンサ、シリアルコネクタなどの離散コンポーネント。 および2V~5V電源。図は、基本的なハードウェア構成を示しています。  ADS113/4/5は、I2Cインターフェイスを介してマスター(マイクロコントローラー)と通信します。 マスターはSCLピンにクロック信号を提供し、データはSDAピンを介して転送されます。 ADS1113/4/5は、SCLピンを決して駆動しません。 使用されているマイクロコントローラーのプログラミングとデバッグについては、デバイス固有の製品データシートを参照してください。 マスターによって送信された最初のバイトは、ADS1113/4/5アドレスに続いて、ADS1113/4/5に後続のバイトを聞くように指示する少しが必要です。 2番目のバイトはレジスタポインターです。レジスタマップについては、表9を参照してください。 マスターから送信された3番目と4番目のバイトは、2番目のバイトに示されているレジスタに書き込まれます。 それぞれ読み取りおよび書き込み操作タイミング図については、図30と図31を参照してください。 ADS1113/4/5を使用したすべての読み取りおよび書き込みトランザクションの前に開始条件が付いていて、停止条件が続く必要があります。 たとえば、ADS1113/4/5を連続変換モードに設定してコンバージョン結果を読み取るには、構成レジスタに書き込むには、次のバイトをこの順序で送信します。 設定レジスタに書き込む: 最初のバイト:0B10010000(最初の7ビットI2Cアドレスとそれに続く低い読み取り/書き込みビット) 2番目のバイト:0B00000001(config Registerのポイント) 3番目のバイト:0B10000100(書き込み対象のconfigレジスタのmsb) 4番目のバイト:0B10000011(書き込み対象のconfigレジスタのLSB) Pointer Registerに書き込む: 最初のバイト:0B10010000(最初の7ビットI2Cアドレスとそれに続く低い読み取り/書き込みビット) 2番目のバイト:0B00000000(変換レジスタのポイント) 変換レジスタを読む: ファーストバイト:0B10010001(最初の7ビットI2Cアドレスとその後の高い読み取り/書き込みビット) 2番目のバイト:変換レジスタのMSBを使用したADS1113/4/5応答 3番目のバイト:コンバージョンレジスタのLSBを使用したADS1113/4/5応答 [目次に戻る] |

| 4.I2Cアドレスの選択 I2Cのアドレスは7bitで値設定はADDRと各ピンを短絡する事により4つのアドレスを設定できる。

|

|||||||||||||||

| 5.レジスター (1)ポインタレジスタ(ポインタレジスタバイトだけRead/Write) ADS1115から特定のレジスタにアクセスするには、まずマスターがポインタレジスタに適切な値を書き込む必要があります。 ポインターレジスタに書き込まれた値によって、4つのレジスタにアクセス出来ます。

レジスタにはポインタレジスタで表している4つのレジスタがある。 変換レジスタ(Conversion Register) 設定レジスタ(Config Register) Lo閾値レジスタ(Lo_thresh REGISTERS) Hi閾値レジスタ(Hi_thresh REGISTERS) 4つのレジスタとアドレス

(2)変換レジスタ (Read/Only) ポインターレジスタ値 0x00 16 ビット レジスタには、最後の変換の結果が 2 進数の 2 の補数形式で格納されます。 リセットまたは電源投入後、変換レジスタは '0' にクリアされ、最初の変換が完了するまで '0' のままになります。 通信では16ビットの上位(BIT15~8)と下位(BIT7~0)の送り順は逆になるので注意すること。

(3)設定レジスタ (Read/Write) ポインターレジスタ値 0x01 16 ビット レジスタを使用して、ADS1113/4/5 の動作モード、入力選択、データ レート、PGA 設定、およびコンパレータ モードを制御できます。 デフォルト設定レジスタ値 8583h 通信では16ビットの上位(BIT15~8)と下位(BIT7~0)の送り順は逆(デフォルト値は8385h)になるので注意すること。

ビット[15] OS: 動作ステータス/シングルショット 変換開始 このビットはデバイスの動作ステータスを決定します。 このビットはパワーダウン モードの場合にのみ書き込むことができます。

ビット [14~12] MUX マルチプレクサ選択 (ADS1115 のみ) MUX[2:0]: 入力マルチプレクサ構成 これらのビットは、入力マルチプレクサを設定します。

[設定レジスタへ戻る] ビット [11:9] プログラマブル ゲイン アンプ選択(ADS1114 および ADS1115 のみ) これらのビットは、プログラマブル ゲイン アンプを設定します。

このパラメータは、ADC スケーリングのフルスケール範囲を表します。 このデバイスに VDD + 0.3V を超える電圧を印加しないでください。 アナログ入力電圧は、絶対最大定格で指定されたアナログ入力電圧制限を決して超えないでください。 4 V を超える VDD 電源電圧を使用する場合、±6.144 V のフルスケール範囲により、入力電圧を電源まで拡張できます。 ただし、この場合 (または電源電圧がフルスケール範囲より低い場合、たとえば、VDD = 3.3 V でフルスケール範囲 = ±4.096 V)、フルスケール ADC 出力コードを取得することはできません。 たとえば、VDD = 3.3 V で FSR = ±4.096 V の場合、VIN = ±3.3 V までの信号のみを測定できます。 この場合、電圧 |VIN| > 3.3 V を表すコード範囲は使用されません。 [設定レジスタへ戻る] ビット[8] MODE: デバイスの動作モード シングル・ショット・モード時は、1回の変換動作後にデバイスの電源が自動的にオフになるため、アイドリング中の消費電力を大幅に低減できます。

ビット [7:5] データレート これらのビットは、データレート設定を制御します。

ビット[4] このビットはコンパレータの動作モードを制御します。(ADS1114 および ADS1115のみ) コンパレータが従来のコンパレータ (COMP_MODE = '0') として実装されるか、ウィンドウ コンパレータ (COMP_MODE = '1') として実装されるかを変更します。ADS1113 では機能しません。

ビット[3] このビットは ALERT/RDY ピンの極性を制御します。(ADS1114 および ADS1115のみ) COMP_POL: コンパレータ極性 (ADS1114 および ADS1115 のみ) COMP_POL = '0' の場合、コンパレータ出力はアクティブ ローです。 COMP_POL='1' の場合、ALERT/RDY ピンはアクティブ ハイです。ADS1113 では機能しません。

ビット[2]このビットは、ALERT/RDY ピンがアサートされたらラッチするか、変換が上限しきい値と下限しきい値のマージン内になったらクリアするかを制御します。 COMP_LAT: ラッチ コンパレータ (ADS1114 および ADS1115 のみ) COMP_LAT = '0' の場合、ALERT/RDY ピンはアサートされてもラッチしません。 COMP_LAT = '1' の場合、アサートされた ALERT/RDY ピンは、変換データがマスターによって読み取られるか、適切な SMBus アラート応答がマスターによって送信され、デバイスがそのアドレスで応答し、それが現在 ALERT/RDY バス ラインをアサートしている最下位アドレスになるまで、ラッチされたままになります。このビットは ADS1113 では機能しません。

ビット [1:0]COMP_QUE: コンパレータ キューと無効化 (ADS1114 および ADS1115 のみ) これらのビットは 2 つの機能を実行します。'11' に設定すると、コンパレータ機能が無効になり、ALERT/RDY ピンがハイ状態になります。他の値に設定すると、ALERT/RDY ピンをアサートする前に必要な上限または下限しきい値を超える連続変換の数を制御します。ADS1113 では機能しません。

[目次に戻る] (4)閾値レジスタ (Read/Write) ポインターレジスタ値 0x02,0x03 Lo_thresh および Hi_thresh レジスタ コンパレータで使用される上限と下限のしきい値は、2 つの 16 ビット レジスタに格納されます。 これらのレジスタは、出力レジスタが値を表示するのと同じ形式で値を格納します。 つまり、2 の補数形式で格納されます。 これはデジタル コンパレータとして実装されるため、PGA 設定が変更されるたびに値を再調整するように特別な注意を払う必要があります。 Hi_thresh レジスタの MSB を「1」に、Lo_thresh レジスタの MSB を「0」に設定することにより、コンパレータ出力ピンの 2 次変換準備機能を実現できます。 ただし、それ以外の場合はすべて、Hi_thresh レジスタは Lo_thresh レジスタよりも大きくする必要があります。 しきい値レジスタのフォーマットを表 10 に示します。 RDY モードに設定すると、ALERT/RDY ピンは、単発モードでは OS ビットを出力し、連続変換モードではパルスを出力します。 Lo_thresh Registers ポインタレジスタ 0x02

Hi_thresh Registers ポインタレジスタ 0x03

[目次に戻る] |

||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

6.注意事項

|