### TC5091AP PENTAPHASIC INTEGRATION 8-DIT A/D CONVERTER

The TC5091AP is a pentaphasic integration 8-bit A/D converter of high precision and low power consumption. The 8-bit output data can be taken out in the form of time-shared higher order 4 bits and lower order 4 bits on four 3-state data output. Either the higher order bits or the lower order bits can be selected by RSEL input. This output system is designed specifically considering interface to 4-bit CPU.

Further, since this converter has an analog multiplexer capable of selecting the input data up to six channels, an over-range flag, and a serial clock output function, it is used for a variety of applications.

#### FEATURES:

- . High precision : ±LSB(Max.)

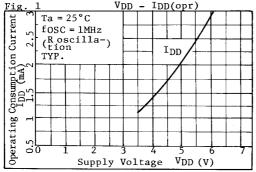

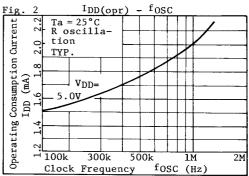

- . Low power consumption: 10mW(Typ.) @(VDD=5V fosc=1MHz)

- . Single power supply : VpD=5±1.5V

- . High-speed conversion: 2ms(Max.) @fosc=1.5MHz

- . 6-channel analog multiplexer contained

- . Reference clock oscillation cirucit contained (CR oscillation)

- . 3-state output with output latch

- . TTL/CMOS compatible digital Input/Output

- . Offset automatic correction

#### APPLICATIONS:

- . Various control instruments (for temperature, humidity, pressure, etc.)

- . Home electric appliances

- . Electrical wiring apparatuses

- . Battery-driven instruments

### ABSOLUTE MAXIMUM RATINGS

| CHARACTERISTIC                 | SYMBOL            | RATING                       | UNIT |

|--------------------------------|-------------------|------------------------------|------|

| DC Supply Voltage              | $v_{\mathrm{DD}}$ | Vss-0.5~Vss+8                | V    |

| Input Voltage                  | VIN               | $V_{SS}-0.5 \sim V_{DD}+0.5$ | V    |

| Output Voltage                 | Vout              | $V_{SS}-0.5 \sim V_{DD}+0.5$ | V    |

| Reference Supply<br>Voltage    | V <sub>REF</sub>  | $V_{AGND} \sim V_{DD} + 0.5$ | V    |

| Analog Ground Voltage          | VAGND             | $V_{SS}-0.5 \sim V_{REF}$    | V    |

| DC Input Current               | IIN               | ±10                          | mA   |

| Power Dissipation              | $P_{\mathrm{D}}$  | 300                          | mW   |

| Operating Temperature<br>Range | Topr              | -40 <b>~</b> 85              | °C   |

| Storage Temperature<br>Range   | Tstg              | <b>-65∼150</b>               | °C   |

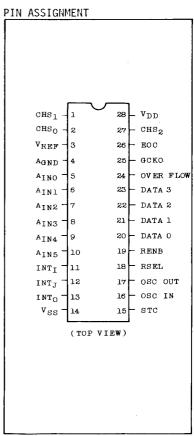

# FUNCTION OF EACH PIN

|         |                 | NAME & FUNCTION                                                                                                         | No.        | SYMBOL           | NAME & FUNCTION                                                                                                            |  |  |

|---------|-----------------|-------------------------------------------------------------------------------------------------------------------------|------------|------------------|----------------------------------------------------------------------------------------------------------------------------|--|--|

| 1 CHS 1 |                 | (Channel Select Inputs) Address inputs to select analog inputs, which consist of three terminals of CHSO <sup>2</sup> . |            | OSC IN           | I/O for reference clocl os-<br>cillation. Clock oscillation<br>can be made by means of ex-<br>ternal registance. Clock can |  |  |

|         |                 | These select inputs are taken into the internal latch by                                                                | 17 OSC OUT |                  | be supplied from outside through input of OSC IN.                                                                          |  |  |

|         |                 | the falling edge of STC inputs. Test mode should not be used.                                                           |            |                  | (Read Select) Input to select the higher order 4 bits or the lower order 4 bits to 4-bit data                              |  |  |

|         |                 | TRUTH TABLE OF MULTIPLEXER  CHS2 CHS1 CHS0 ON channel                                                                   | 18         | RSEL             | output. "H": Output of the higher                                                                                          |  |  |

|         | _               | L L L VREF* L L H AGND* L H L AINo                                                                                      |            |                  | order 4 bits. "L": Output of the lower order 4 bits.                                                                       |  |  |

| 2       | CHS 0           | $ \begin{array}{c ccccccccccccccccccccccccccccccccccc$                                                                  | 19         | RENB             | (Read Enable) Data read signal. "H": The data 0 ∿ 3 and over flow can be output. "L": The output above is at               |  |  |

|         |                 | * Test Conditions                                                                                                       | 20         |                  | high impedance.                                                                                                            |  |  |

|         |                 | (Reference Voltage) Reference voltage supplying                                                                         |            | DATA 0<br>DATA 1 | (3-state Parallel Data Outputs)<br>Conversion data output.                                                                 |  |  |

| 3       | $v_{REF}$       | terminal, which performs as full-scale voltage of AIN.                                                                  | 22         | DATA 2<br>DATA 3 | The data 0 is LSB, and the data 3 is MSB.                                                                                  |  |  |

| 4       | AGND            | (Analog Ground) Electrical potential to deter- mine "zero point" of AIN.                                                | 24         | OVER-<br>FLOW    | In case of overrange or underranbe, "H" level is output and the output is 3-state output.                                  |  |  |

| 5       | AIN 0           | (Analog Input) Analog input terminals, by                                                                               |            | -                | (Gated Clock Output)                                                                                                       |  |  |

| 7       | AIN 2           | which AIN selected by CHS                                                                                               | 25         |                  | Pulses of number equivalent to                                                                                             |  |  |

| 8       |                 | inputs are integrated. Input voltage range is AGNDVVREF.                                                                |            | GCKO             | the conversion data are out-<br>put during conversion                                                                      |  |  |

| 10      | AIN 5           |                                                                                                                         |            |                  | (356 pulses at full scale)                                                                                                 |  |  |

| 11      | INT I           | (Integrator Input, Integrator Junction, Integrator Output)                                                              | 26         | EOC              | (End of Conversion) Conversion endig signal, EOC goes to "L" level at the fall                                             |  |  |

| 12      | INT J           | tornal register Pr and ev-                                                                                              |            | EUC              | of STC, and returns to "H"                                                                                                 |  |  |

| 13      | INT O           | ternal resistor $R_{\rm I}$ and external capacitor $C_{\rm I}$ .                                                        |            |                  | level at the end of conversion.                                                                                            |  |  |

| 14      | V <sub>SS</sub> | (Digital Ground)<br>Normally OV                                                                                         | 27         | CHS 2            | (Channel Select Input) Refer to Pins 1 and 2.                                                                              |  |  |

| 15      | STC             | (Start Conversion) Conversion starting signal. Conversion starts at the fall- ing edge.                                 | 28         | VDD              | (Power Supply)<br>5V ± 1.5V                                                                                                |  |  |

### FUNCTIONAL DESCRIPTION

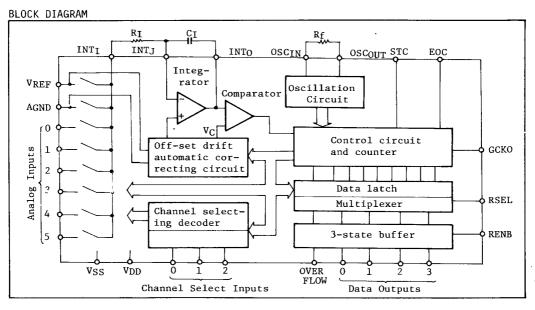

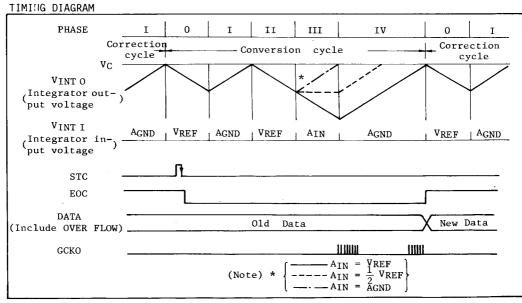

#### (1) System Description (Pentaphasic Integration)

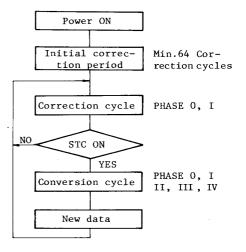

The operation of the TC5091AP is composed of the correction cycle and the conversion cycle as shown in the timing chart. While the power is switched on, the repetition of correction cycle and conversion cycle enables the TC5091AP at make A/D conversion under the optimum conditions at all times. The operation flowcahrt is shown in Fig. 1.

#### (a) Initial correction period

The internal state of this LSI is reasonably unsettled at the time when the power is switched on;

Fig. 1 Operation Flowchart

therefore, the initial correction cycle is requires before stable coverting operation becomes possible.

The correction cycle automatically corrects conversion error caused by offset voltage of the integrator or the like, and is composed of the period (PHASE 0) for which VREF is integrated and the period (PHASE I) for which AGND is integrated.

Since system correction is performed in steps at the end of this PHASE I, 64 correction cycles (64  $\times$  1024  $\cdot$  T<sub>OSC</sub>) are required as the initial correction period. (ToSC denotes one clock cycle.)

#### (b) Conversion cycle

If the initial correction cycle period is completed, normal conversion becomes possible.

When STC input is given, (although the correction cycle in PHASE 0 or PHASE I is in operation at this time), the correction operation stops, and the conversion cycle starts.

In other words, even if STC input is given, this LSI performs the same operation as the correction cycle until PHASE I is completed; but it does not perform the correction at the time of completion of PHASE I, and shifts to PHASE II. Therefore, attention should be given to the fact that PHASE I prior to PHASE II does not act as correction cycle.

When STC input is given, the LSI integrates analog input in PHASE III through PHASE I and PHASE II, performing digital conversion in PHASE IV. When the LSI completes digital conversion in PHASE IV, the output is turned to the new data and the LSI returns to the correction cycle.

## (c) Correction cycle

When the next STC input is given between completion of arbitrary conversion cycle (at the time of completion of PHASE IV) and completion of one correction cycle (1024·ToSC), no correction is substantially made. Therefore, in case the STC input is consecutively given, another STC should be given after the lapse of one correction cycle at the earliest from completion of PHASE IV. When the STC input is given during conversion (While EOC is at "L" level), the STC cannot be accepted.

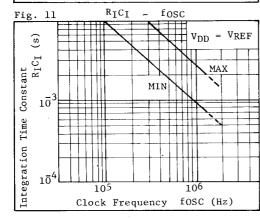

# (d) Constant of integration

The  $R_{\rm I}$  and  $C_{\rm I}$  composing the integrator should be selected to satisfy the following equation.

$$R_{I}C_{I} = (0.9 \sim 2.5) \cdot \frac{V_{REF}}{V_{DD}} \cdot \frac{103}{f_{OSC}}$$

[S]

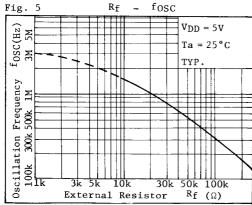

Attention should be paid to the fact that, when the external R oscillation is used, fosc has  $\pm 30\%$  variations in regard to the typ. value in Fig. 5 due to variations in sample and temperature characteristic.

In other words, if the typ. value in Fig. 5 is denoted by  $f_R$ -TYP, the  $R_I$  and  $C_I$  should be selected according to the following equation.

$$R_{\rm I}C_{\rm I} = (1.2 \, 1.75) \cdot \frac{V_{\rm REF}}{V_{\rm DD}} \cdot \frac{10.3}{f_{\rm R} \cdot Typ}$$

[S]

# (2) Output Data Mode

### TRUTH TABLE

|      |                                                        | DIGITAL OUTPUTS |                 |      |      |       |      |      |      |      |

|------|--------------------------------------------------------|-----------------|-----------------|------|------|-------|------|------|------|------|

| RENB | ANALOG INPUT                                           |                 | RSEL = "H"      |      |      |       | OVER |      |      |      |

| KEND | ANALOG INFO                                            | DATA            | DATA            | DATA | DATA | DATA  | DATA | DATA | DATA | FLOW |

|      |                                                        | 0               | 1               | 2    | 3    | 0     | 1    | 2    | 3    | l    |

| L    | Don't Care                                             |                 |                 |      | High | Imped | ance |      |      |      |

| Н    | $\sim \frac{1}{2}$ LSB                                 | L               | L               | L    | L    | L     | L    | L    | Ĥ.   | н    |

| н    | $\frac{1}{2}$ LSB $\sim \frac{1}{2}$ LSB               | L               | L               | L    | L    | L     | L    | L    | L    | L    |

| н    | $\frac{1}{2}$ LSB $\sim \frac{3}{2}$ LSB               | Н               | L               | L    | L    | L     | L    | L    | L    | L    |

| н    |                                                        |                 | Straight Binary |      |      |       |      |      |      |      |

| Н    | "FS"- $\frac{5}{2}$ LSB $\sim$ "FS"- $\frac{3}{2}$ LSB | L               | Н               | Н    | Н    | Н     | Н    | Н    | Н    | L    |

| Н    | "FS"- $\frac{3}{2}$ LSB $\sim$ "FS"- $\frac{1}{2}$ LSB | Н               | Н               | Н    | н    | Н     | Н    | Н    | Н    | L    |

| Н    | "FS"- $\frac{1}{2}$ LSB $\sim$                         | Н               | Н               | Н    | Н    | Н     | Н    | н    | Н    | Н    |

8-bit digital data is output on four data lines after having been divided into the higher order 4 bits and the lower order 4 bits. Either the higher order bits or the lower order bits can be selected by RSEL.

## (3) System Clock Oscillation Circuit

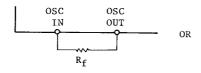

For oscillating reference clock the oscillation circuit is composed of external resistors as shown in Fig. 2.

OSC OSC OUT

OUT

External Clock

Fig. 2 Clock Supplying Methods

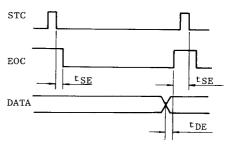

- (4) Timings for STC-EOC and EOC-DATA

- o Time (tsE) from the fall of STC to the fall of EOC.

$$t_{SE} = \frac{1}{2} T_{OSC} \sim \frac{3}{2} T_{OSC}$$

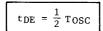

o Time ( $t_{DE}$ ) from the out of DATA output to the rise of EOC

Fig. 3 Timing Chart of STC, EOC

0 Min. time ( $t_{\rm ES}$ ) from the rise of EOC to the acceptance of another STC.

$$t_{\rm ES} = \frac{1}{2} T_{\rm OSC} \sim \frac{3}{2} T_{\rm OSC}$$

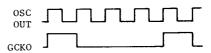

# (5) GCKO Output (Gated Clock Output)

During the conversion (PHASE IV), the pulses of number equivalent to the values of digital data can be obtained on GCKO output.

The output pluse has the frequency corresponding to four times of reference clock as shown in Fig. 4, and is synchronized with the rising edge of OSC OUT.

Fig. 4 Timing Chart of GCKO Output

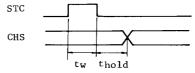

# (6) Timing for STC Input and CHS Input

STC signal is taken in synchronously with the internal clock. Therefore, if  $T_{OSC}$  denotes one clock cycle of OSC terminal, the pulse width of more than  $(2 \cdot T_{OSC})$  is required.

Fig.5 Timing Chart of Control Input

Since the data of CHS $_{0\sim2}$  are also latched in synchronously with the internal clock, the CHS signal at least requires the hold time of ( $T_{\rm OSC}$  + 50ns) or more after the fall of STC.

NOTE:

$$t_w > 2 \cdot T_{OSC}$$

,  $t_{hold} > T_{OSC} + 50 \text{ns}$

## RECOMMENDED OPERATING CONDITIONS (VSS = OV)

| ITEM                   | SYMBOL |          | MIN. | TYP. | MAX.        | Unit      |

|------------------------|--------|----------|------|------|-------------|-----------|

| Supply Voltage         | VDD    |          | 3.5  | 5    | 6.5         | V         |

| Input Voltage          | VIN    |          | 0    |      | VDD         | V         |

| Reference Voltage      | VREF   | _        | 3    | -    | $v_{ m DD}$ | v         |

| Analog Ground Voltage  | VAGND  |          | 0    | 0    | 1           | V         |

| Integral Resistor      | RI     |          | 0.4  | _    | 2           | $M\Omega$ |

| Integral Capacitor     | CI     | (Note)   | - 1  | -    |             |           |

| Oscillatory Resistance | Rf     | VDD = 5V | 10   | -    | -           | MΩ        |

Note: Refer to the operating consideration (1) for determing the values of  $R_{\rm I}$  and  $c_{\rm I}$  respectively. The ripples of VpD and  $^{\rm V}_{\rm REF}$  should be held down to less than 1/256 of the respective absolute values in view of precision.

# ELECTRICAL CHARACTERISTICS (VSS = 0V)

| ITEM                                      | SYM-                      | TEST                                                                         | $v_{DD}$ | -40°C |      | 25°C |                   |              | 85°C |            | TINTE      |

|-------------------------------------------|---------------------------|------------------------------------------------------------------------------|----------|-------|------|------|-------------------|--------------|------|------------|------------|

| BOL                                       |                           | CONDITION                                                                    | (V)      | MIN.  | MAX. | MIN. | TYP.              | MAX.         | MIN. | MAX.       | UNIT       |

| Output High Voltage                       | voH                       | IOUT <1 µA<br> VIN=VSS,VDD                                                   | 5        | 4.95  | _    | 4.95 | 5.00              | -            | 4.95 | -          | v          |

| Output Low Voltage                        | v <sub>OL</sub>           | IOUT   <1 μA<br>VIN=VSS, VDD                                                 | 5        | _     | 0.05 | -    | 0.00              | 0.05         | _    | 0.05       | 1 "        |

| Output High Current                       | I <sub>OH</sub>           | V <sub>OH=4.0V</sub><br>V <sub>IN=VSS</sub> ,V <sub>DD</sub> *               | 5        | -1.2  | -    | -1.0 | -2.0              | _            | -0.7 | -          | mA         |

| Output Low Current                        | IOL                       | V <sub>OL</sub> =0.4V<br>V <sub>IN</sub> =V <sub>SS</sub> ,V <sub>DD</sub> * | 5        | 2.4   | _    | 2.0  | 4.0               | -            | 1.6  | _          | m.A.       |

| Input High Voltage                        | $v_{IH}$                  | *                                                                            | 5        | 2.4   | -    | 2.4  | -                 | _            | 2.4  | -          | v          |

| Input Low Voltage                         | $v_{\mathrm{1L}}$         | *                                                                            | 5        | -     | 0.8  | _    | _                 | 0.8          | _    | 0.8        |            |

| Output Disable<br>Current                 | I <sub>DH</sub>           | V <sub>OH</sub> =6.5V<br>V <sub>OL</sub> =0V                                 | 6.5      | _     | ±0.5 | -    | ±10 <sup>-4</sup> | <b>±0.</b> 5 | -    | <b>±</b> 5 |            |

| Input Current                             | IIH                       | V <sub>IH</sub> =6.5V *                                                      | 6.5      | -     | ±0.3 | -    | ±10 <sup>-5</sup> | ±0.3         | _    | ±1         | μ <b>A</b> |

| Analog Switch<br>Input Leak Current       | ı <sub>off</sub>          | V <sub>IH</sub> =6.5V<br>V <sub>IL</sub> =0V                                 | 6.5      | _     | ±0.3 | -    | ±10 <sup>-5</sup> | ±0.3         | -    | ±1         |            |

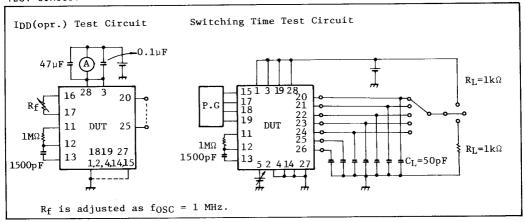

| Operating Con-<br>sumption Current        | I <sub>DD</sub><br>(opr.) | fosc=1 MHz                                                                   | 5        | _     | _    | _    | 1.8               | 3            | _    | _          | mA         |

| Reference Supply Con-<br>sumption Current | I REF                     | VREF = 5V<br>AGND = 0V                                                       | 5        | _     | -    | -    | 0.3               | 0.6          | _    | _          |            |

<sup>\*</sup> Applicable to digital input/output. Not applicable to analog input/output and  ${\rm OSC_{IN}/OSC_{OUT}}$ .

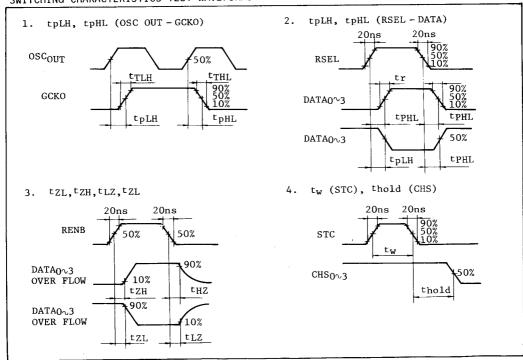

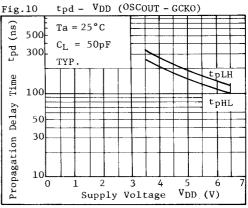

SWITCHING CHARACTERISTICS ( $^{V}DD = 5V$ ,  $^{V}SS = 0V$ ,  $^{T}a = 25$  $^{\circ}C$ ,  $^{C}L = 50$  $_{P}F$ )

| ITEM                                   | SYMBOL           | TEST CONDITION                  | MIN. | TYP.        | MAX. | UNIT       |

|----------------------------------------|------------------|---------------------------------|------|-------------|------|------------|

| Output Rise Time                       | tTLH             |                                 | -    | <b>'</b> 50 | 100  |            |

| Output Fall Time                       | tTHL             | é                               | -    | 40.         | 100  |            |

| (Low-High) Propaga-<br>tion Delay Time | t <sub>pLH</sub> | OSCOUT-GCKO                     | -    | 200         | 400  |            |

| (High-Low) Propaga-<br>tion Delay Time | $t_{ m pHL}$     | OSCOUT-GCKO                     | -    | . 150       | 400  |            |

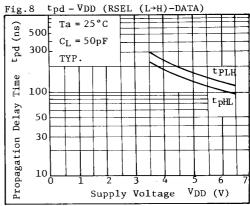

| (Low-High) Propaga-<br>tion Delay Time | t <sub>pLH</sub> | RSEL("L"→"H")-DATA OUT          | -    | 180         | 400  |            |

| (High-Low) Propaga-<br>tion Delay Time | t <sub>pHL</sub> | RSEL( L -> H )-DATA OUT         |      | 150         | 400  | ns         |

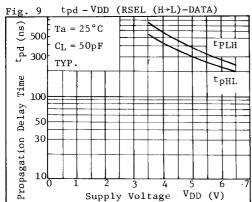

| (Low-High) Propaga-<br>tion Delay Time | t <sub>PLH</sub> | DON'T (HAND HAND) DAME OVER     | -    | 380         | 700  |            |

| (High-Low) Propaga-<br>tion Delay Time | t <sub>pHL</sub> | RSEL("H"→"L")-DATA OUT          | - '  | 300         | 700  |            |

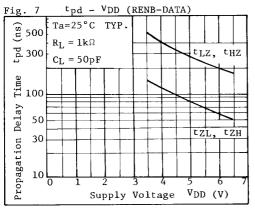

| Output Enable Time                     | tZL<br>tZH       |                                 | _    | 80          | 250  |            |

| Output Disable Time                    | tLZ<br>tHZ       |                                 | -    | 280         | 500  | ,          |

| Max. Clock Frequency                   | fMAZØ            | OSC Input                       | 1.5  | 3.0         | -    | MHz        |

| Min. Clock Frequency                   | fminø            | OSC Input                       |      | _           | 100  | kHz        |

| Input Capacity                         | CIN              | Digital Input                   | _    | 4           | -    | p <b>F</b> |

| Analog Input Capacity                  |                  | A <sub>0</sub> ∿ A <sub>5</sub> | -    | 7           | _    | рF         |

| 3-State Output Capacity                | COUT             |                                 | _    | 8           | -    | pF         |

# SYSTEM CHARACTERISITCS (Ta = -40 \sigma 85 °C)

| I TEM                | SYMBOL              | TEST CONDITION                          | MIN.                   | TYP.              | MAX.                                    | UNIT |

|----------------------|---------------------|-----------------------------------------|------------------------|-------------------|-----------------------------------------|------|

| Zero Point Error     | EZP                 |                                         | _                      | $\pm \frac{1}{4}$ | ± 1/2                                   |      |

| Full Scale Error     | EFS                 | $V_{REF} = V_{DD} = 5V$ $V_{AGND} = 0V$ | _                      | $\pm \frac{1}{4}$ | ± 1                                     | LSB  |

| Nonlinearity         |                     | -                                       | _                      | ± 1/4             | ± 1                                     |      |

| STC Min. Pulse Width | tw                  |                                         | _                      | _                 | 2<br>fosc                               | s    |

| CHS Min. Hold Time   | thold               | STC = CHS <sub>0</sub> ∿2               | -                      | · <b>-</b>        | $\frac{10}{\text{fosc}}$ +50            | ns   |

| Conversion Time      | t <sub>conv</sub> . | $A_{IN} = 0 \sim FS$                    | $\frac{10^3}{f_{OSC}}$ | -                 | 3.1x10 <sup>3</sup><br>f <sub>OSC</sub> | s    |

<sup>\*</sup> fosc : OSC terminal clock frequency [Hz], FS : Full Scale voltage,  $v_{DD}$  level

### TEST CIRCUIT

# SWITCHING CHARACTERISTICS TEST WAVEFORMS

#### STANDARD CHARACTERISTICS CHARTS

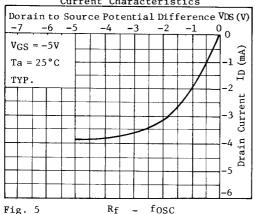

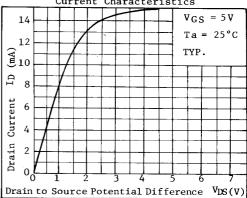

Fig. 3 P-channel Output Buffer Drain

Current Characteristics

Fig. 4 N-channel Output Buffer Drain Current Characteristics

(Note)

The characterisitcs at left have been prepared for reference at the time of determination of an integrator time constant according to the equation of

$$(R_{I}C_{I} = (0.9 \sim 2.5) \cdot \frac{v_{REF}}{v_{DD}} \cdot \frac{103}{f_{OSC}}(s))$$

for determing R<sub>I</sub>·C<sub>I</sub>.

In case of the determination of  $R_{\rm I}$  and  $C_{\rm I}$ , the product, or the value, of  $R_{\rm I}$  and  $C_{\rm I}$  is required to be within the range of MIN. to MAX. as shown in left figure after due consideration of dispersion.